量子計算機芯片,爲什麼這麼難造?

在當今數字世界中,RSA‑2048 與 ECC 等經典公鑰密碼是最廣泛應用的加密標準,支撐着網絡安全、金融交易和隱私保護的底層信任。然而,這一基石正面臨量子計算的潛在威脅。

理論上,量子計算機能夠以遠快於經典計算機的速度分解大整數和離散對數求解,從而在短時間內破解 RSA 和 ECC 加密。這一前景既令人興奮,也令人擔憂。

問題在於,量子計算機的發展究竟到了什麼階段?有人樂觀地認爲經典公鑰密碼的“倒計時”已經開始;也有人懷疑,受限於製造難度,真正可用的量子計算機還遙遙無期。市面上相關論調不一,往往樂觀或悲觀,但核心疑問始終縈繞:量子計算機距離破解經典公鑰密碼還有多遠?

而這個問題的答案,跟“量子芯片”相關技術的發展密切相關。簡單地說,就是沒有金剛鑽,難做瓷器活,芯片性能達不到,用量子計算機破解那些經典的公鑰密碼也就無從談起。然而,想做出強大的量子芯片,卻困難重重。

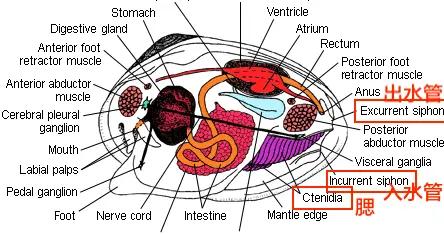

量子芯片,也就是放置量子比特(約瑟夫森結)的芯片,又稱量子處理器。要構造更多量子比特的芯片,主要會遇到三個難題:佈線問題、串擾問題和半導體良品率問題。

佈線問題

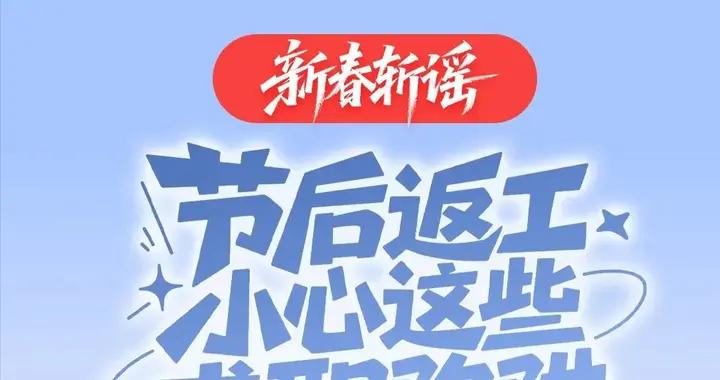

由於每個量子比特都需要引出多根線纜(比如控制線、讀出線),同時量子比特與比特之間還需要有耦合器(類似於開關)互聯。

在二維芯片上,當量子比特數量增加時,佈線複雜度會非線性增加。特別是當需要實現高連接度時,中心區域的比特控制線必須繞過外圍比特,導致芯片面積急劇增加。

圖 1 隨着量子比特數量增加,佈線複雜度呈非線性增長

串擾問題

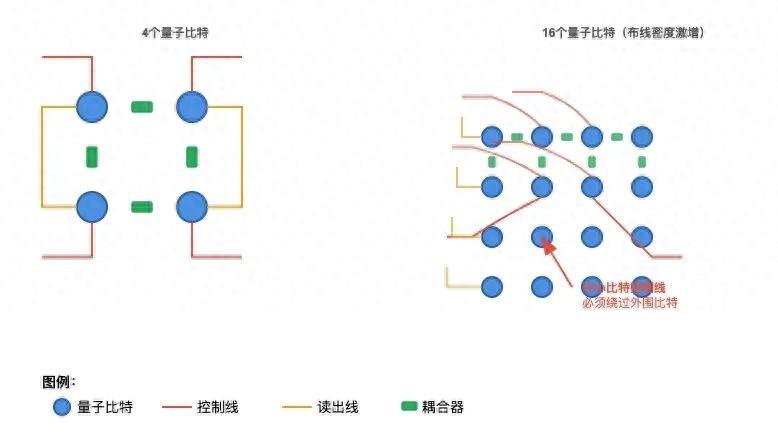

串擾指的是量子比特之間的互相干擾,會導致量子態退相干,並且隨着比特數量的增加呈非線性增強。常見的串擾可以分爲:

· 經典串擾:量子比特的控制信號的頻率靠的太近,導致控制相互干擾。(頻率指的是波每秒完成的週期數。在量子計算中,每個量子比特通過不同頻率的微波信號進行控制,從而實現精確的操作和調控)

· 量子串擾:本應關閉的比特耦合沒有完全關斷;(類比到經典電路則是斷開開關之後仍然還有電流通過)

· 全局串擾:來自外部環境的未知物理過程的串擾,比如宇宙射線,聲子傳播等

要避免串擾,一方面可能需要更大的隔離區或精心設計的屏蔽結構,另一方面也可以在器件層面優化耦合器(coupler)的性能,讓比特間的耦合開關得以更徹底地關斷。此外,改進測控系統,尤其是頻率分配的優化,也有助於降低並行執行雙比特門時的串擾。

圖 2 串擾隨量子比特數量增加呈非線性增強,嚴重影響量子態相干性。

器件良品率問題

如果單從面積來看,量子芯片的面積應該和量子比特數量成線性關係。但由於要處理佈線和串擾問題,實際芯片面積往往會隨着量子比特的數量增長,且顯著超線性,接近平方增長。也就是說,量子比特越多,芯片面積就會非線性地放大。

更麻煩的是,量子比特對缺陷極其敏感,哪怕 1% 的失敗率都會讓整個系統不可用。如果芯片內部或者表面存在缺陷,就可能與量子比特發生耦合,降低其相干時間。

而在微納加工領域存在一個基本規律,芯片面積越大,良品率越低,大面積芯片的製造難度會呈指數增加。對於超導量子芯片來說,雖然其製造過程可以借用半導體工業的成熟設備和工藝流程,但量子比特對製造缺陷的極端敏感性使得良品率問題成爲一個巨大的挑戰。

圖 3 面積隨着量子比特數量以接近N²增長,而良品率隨面積指數下降。圖中概率值僅作演示,非真實值。

希望的曙光:模塊化設計與片間互聯

佈線、串擾和良品率的問題,都會隨着量子比特數量的增加而非線性惡化。因此,如果直接在一塊芯片上構造百萬量子比特,幾乎是不可能的。

於是出現了新的思路:先構造數千個物理量子比特的小芯片(Chiplet)模塊(這樣就能組成一個可靠的邏輯量子比特),再通過片間互聯技術把這些小芯片連接起來。這樣一來,單片的工程挑戰只是從數百擴展到數千,難度大幅降低,也更加可行。

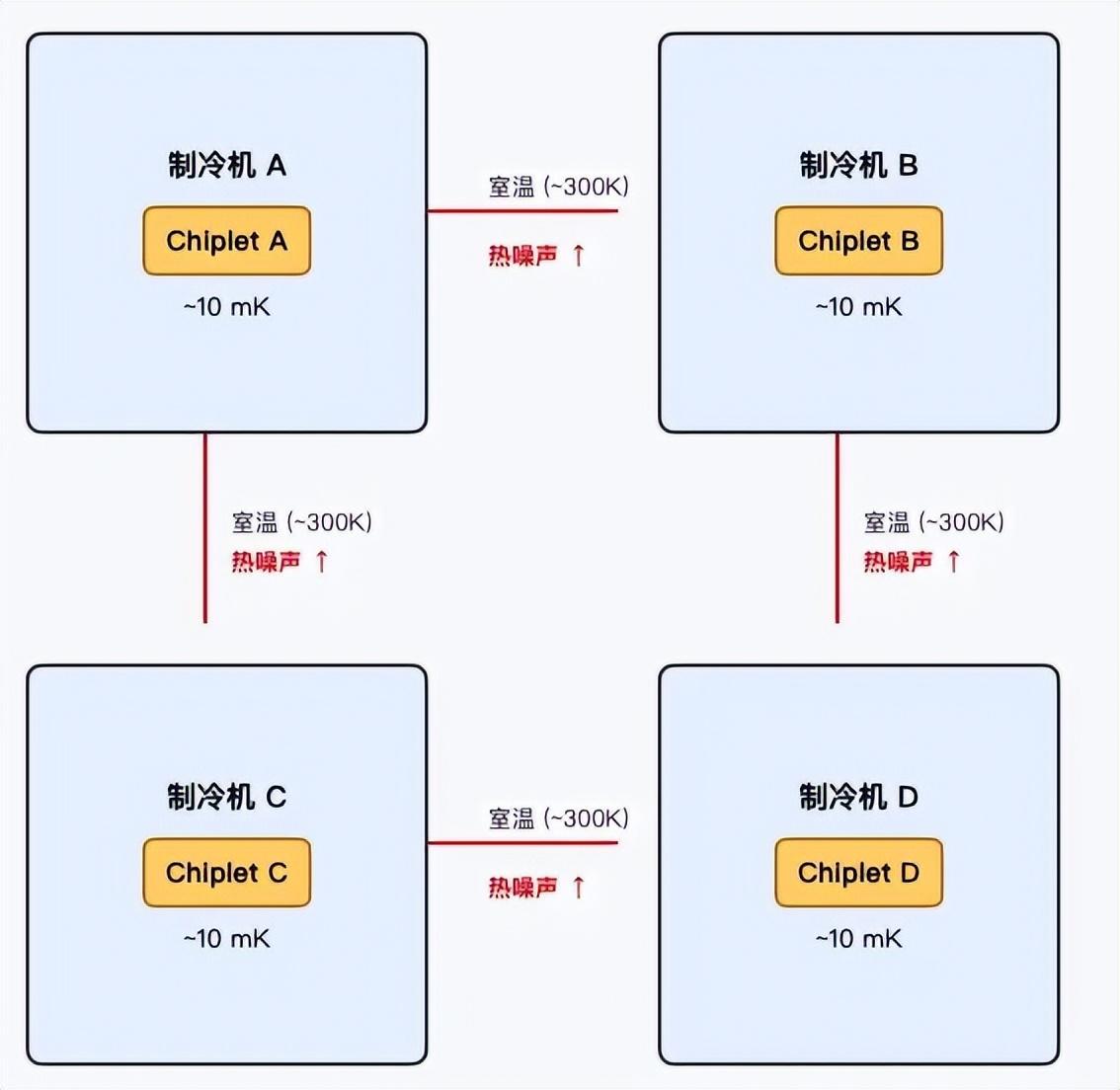

不過,這個思路也帶來了新問題。量子比特非常脆弱,必須放在 10 毫開爾文左右的低溫環境裏工作。如果將每個 Chiplet 分別放置在獨立的稀釋製冷機中,那麼爲了實現 Chiplet 之間的互聯,就需要將信號線從一個製冷機的低溫環境引出到室溫,再進入另一臺製冷機的低溫環境。

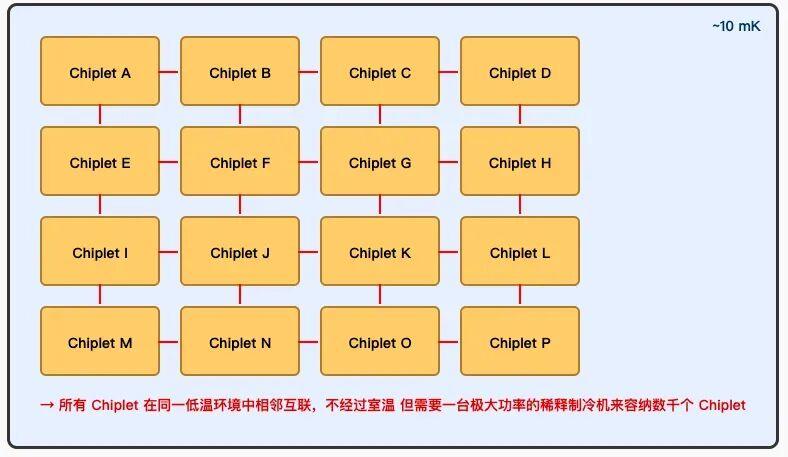

這種“低溫 ↔ 室溫 ↔ 低溫”的信號傳輸路徑會引入較大的熱負載和噪聲,從而破壞量子比特的狀態。如果所有 Chiplet 都放在同一臺稀釋製冷機裏,那我們就需要一臺功率極其龐大的稀釋製冷機來容納數千個 Chiplet,而製造這樣的大規模稀釋製冷機本身就是全新的挑戰。

圖 4 Chiplet跨稀釋製冷機互聯會引入額外熱噪聲,需要注意的是,實際的互聯拓撲並不一定是相鄰 Chiplet 兩兩直接連接。圖中所示的相鄰互聯方式僅用於演示。

圖 5 稀釋製冷機示意圖

多個 Chiplet 被放置在同一稀釋製冷機內,並在低溫環境下直接互聯。這種集中式方案意味着需要一臺超大功率的稀釋製冷機 來容納並維持大量 Chiplet 的工作溫度。需要注意的是,實際的互聯拓撲並不一定是相鄰 Chiplet 兩兩直接連接,圖中所示的相鄰互聯方式僅用於演示。

因此,未來要麼找到新的辦法來抑制跨稀釋製冷機互聯的噪聲,要麼就得在稀釋製冷機的規模化上突破。就目前的科學和工程現狀來看,後者,即研發更大功率、更大空間的低溫稀釋製冷機,似乎是更可行的方向。

總結

如果採用 Chiplet 設計 + 片間互聯的方案,那麼在量子芯片層面上需要跨越的 gap,就是如何把單片量子比特從數百擴展到數千。

好消息是,半導體已經是一棵“點亮的科技樹”,相關工藝還在持續進步。比如,可以借鑑先進封裝中的 3D 堆疊工藝來製造量子芯片,從而提高佈線密度和互聯能力。同時,超導材料工藝的優化、多路複用設計、芯片架構設計的改進(如更高效的耦合器、更合理的頻率規劃)也都會幫助我們突破這一關口。

所以,單個小芯片從數百到數千個物理量子比特這一階段,難度雖然不小,但這一步主要還是工程瓶頸,整體上看起來還是比較樂觀的。目前,IBM 已造出了單片擁有 1000 個物理量子比特的芯片,不過由於芯片面積很大,將不可避免的面臨量產時良品率以及芯片內量子比特可靠性的挑戰。也正因爲目前種種技術所限,暫時還製造不出能夠破解 RSA‑2048 的百萬量子比特計算機,不過業界普遍認爲,到 203X 年,我們也許能夠見證這種量子計算機的誕生。

策劃製作

本文爲科普中國·創作培育計劃扶持作品

出品丨中國科協科普部

監製丨中國科學技術出版社有限公司、北京中科星河文化傳媒有限公司

作者丨李冠成 騰訊玄武實驗室

審覈丨欒春陽 國防科技大學理學院

策劃丨張林林

責編丨丁崝

審校丨徐來、張林林